Northwest-AI-Hub at the Commons Annual Meeting 2024

Representatives from the California-Pacific-Northwest AI Hardware Hub (led by Stanford University) and our partners from the University of California, Berkeley, University of California,Davis, University of Washington, Oregon State University, University of Hawaii at Manoa, and Western Digital descended on Washington DC for the joint Microelectronics Commons Annual Meeting & NSTC Symposium on October 28- 30, 2024 at the historic Omni Shoreham Hotel.

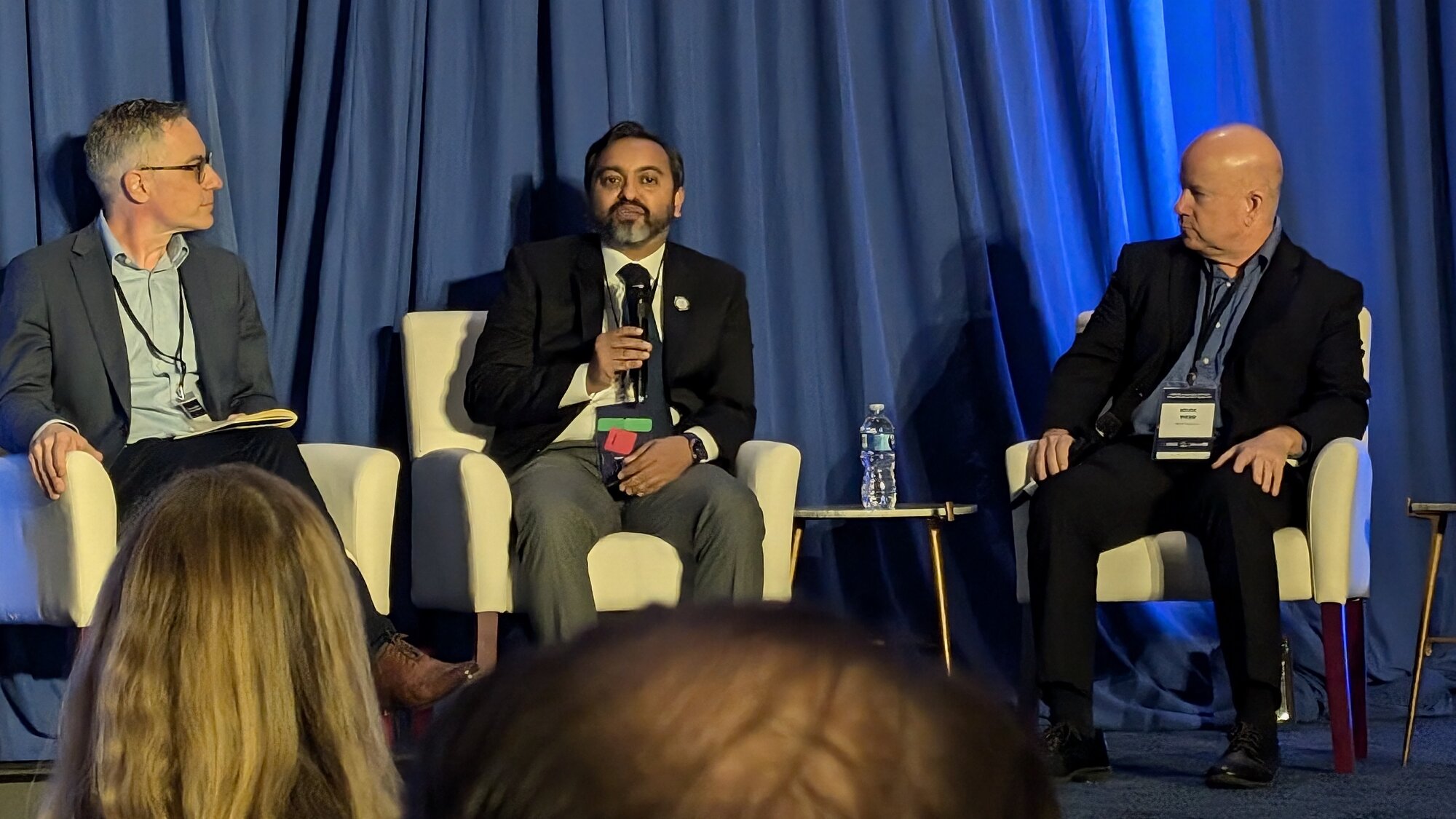

On the first day of the NSTC Symposium, Professor Sayeef Salahuddin, TSMC Distinguished professor of Electrical Engineering and Computer Sciences from the University of California, Berkeley shared his expertise during the panel discussion for R&D Topic 1: The Semiconductor R&D Landscape: Needs and Opportunities.

During the recent DoD multi-Hub project announcements at Arizona State University, the Northwest-AI-Hub was awarded 3 projects, all related to AI Hardware. During the Projects session on the second day of the meeting, October 29, Professor Subhasish Mitra, Professor Ben Yoo, and Professor Sayeef Salahuddin had the opportunity to discuss their projects:

Project G057-01: Energy-Efficient and Scalable AI Hardware Systems through Heterogeneous Integration of Specialized Chiplets

Lead: Subhasish Mitra, William E. Ayer Professor in the Departments of Electrical Engineering and Computer Science at Stanford University

Description: This project will use innovations in semiconductor materials, integration technologies and AI system architecture to drastically improve energy consumption and performance of AI hardware. Interconnected heterogeneous chiplets, built using leading-edge CMOS and 3D CMOS+X semiconductor technologies such as carbon nanotube transistors, resistive memory, and oxide semiconductors, form the foundation for such AI systems.

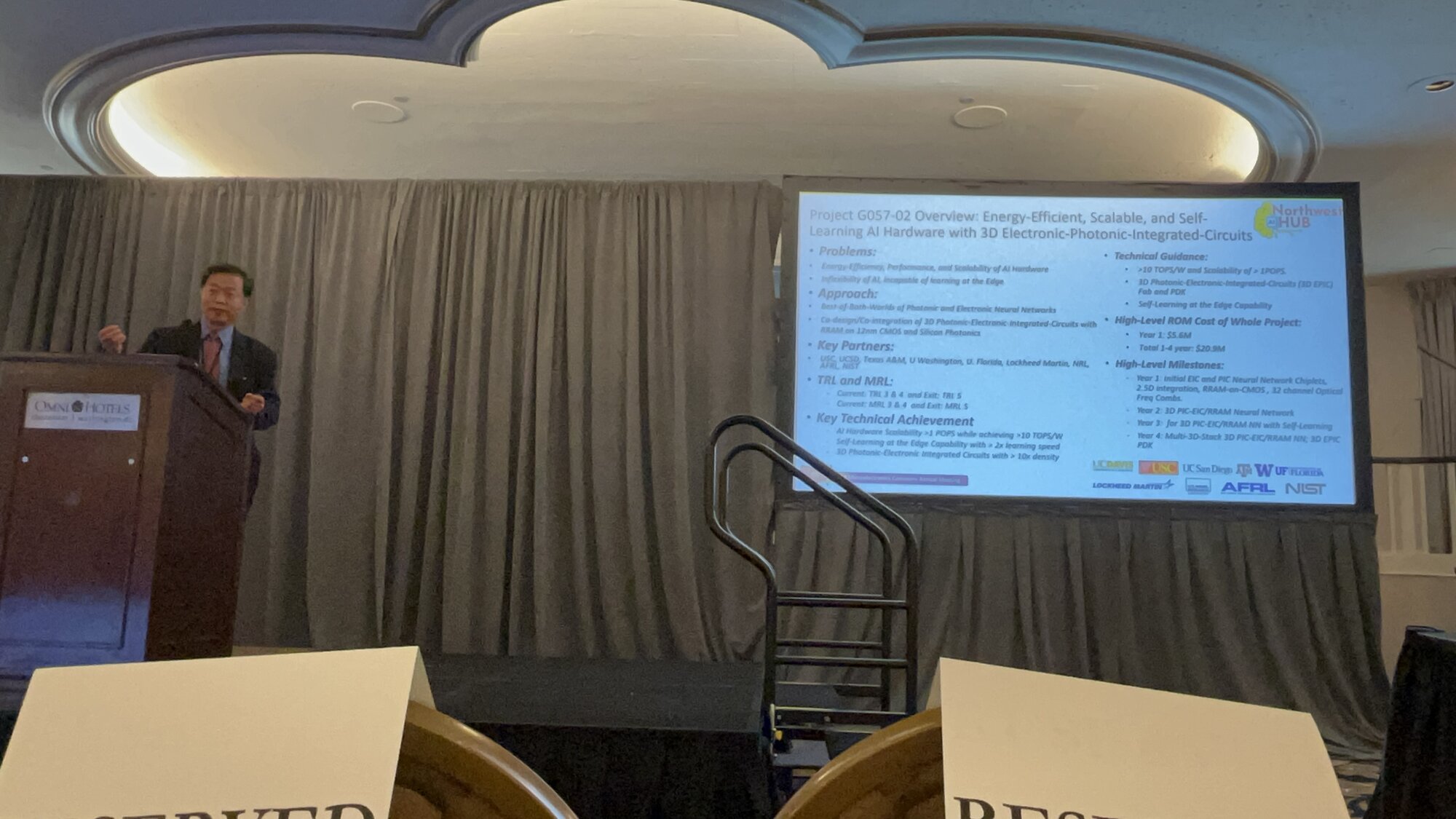

Project G057-02: Energy-Efficient and Scalable, and Self-learning AI Hardware with 3D Electronic-Photonic-Integrated-Circuits

Lead: S. J. Ben Yoo, Distinguished Professor of Electrical and Computer Engineering at the University of California, Davis

Description: This project aims to demonstrate commercially viable and multi-purpose optoelectronic AI computing prototypes that will address large-scale AI challenges at the chip scale. This project plans to combine “best-of-both-worlds” innovations in photonics and electronics, integrating them into a compact 3D circuit module.

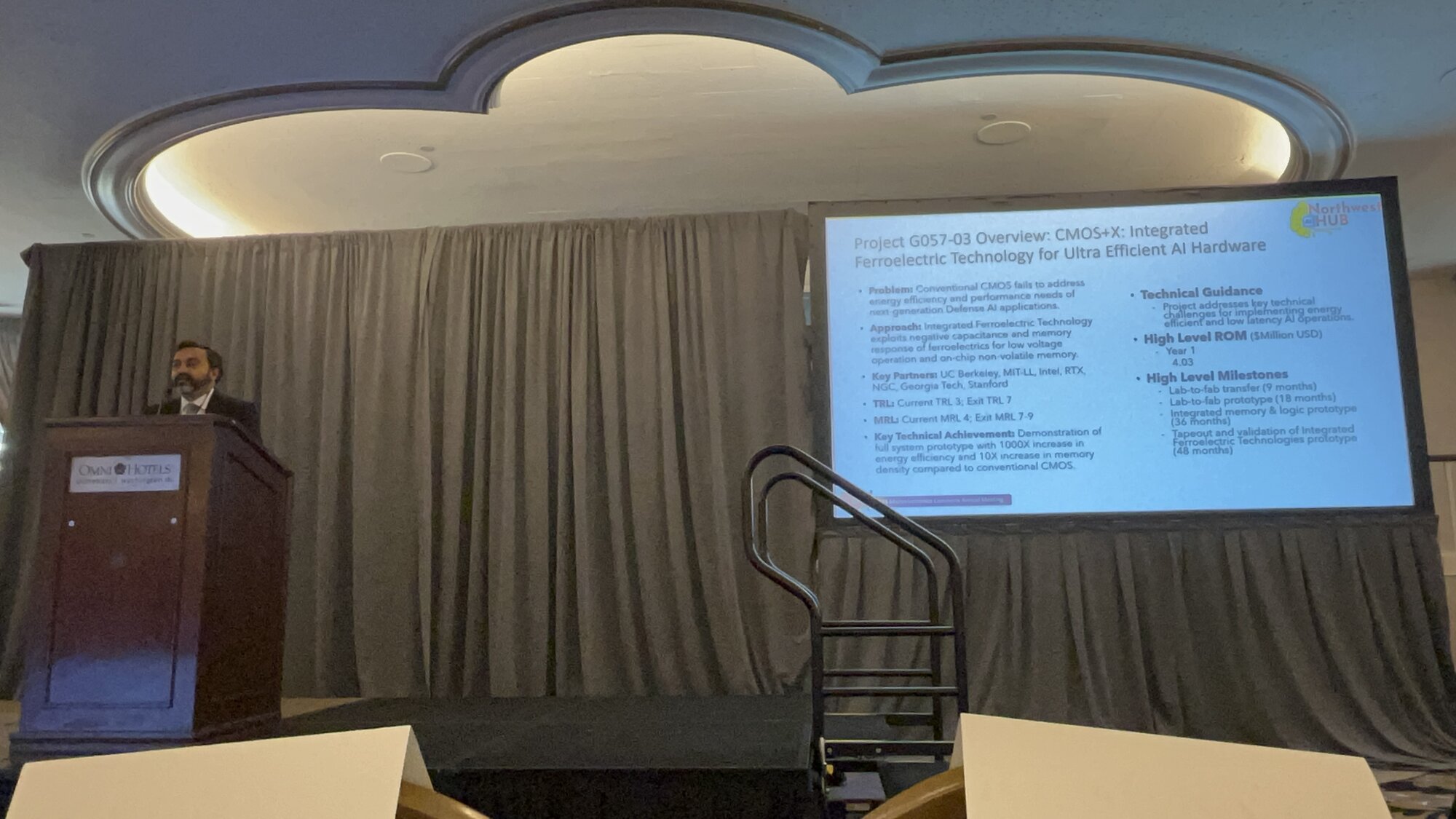

Project G057-03: CMOS+X: Integrated Ferroelectric Technologies for Ultra Efficient AI Hardware

Lead: Sayeef Salahuddin, TSMC Distinguished Professor of Electrical Engineering and Computer Sciences at the University of California, Berkeley

Description: This project aims to substantially improve energy efficiency for future AI hardware by exploiting unique properties of ferroelectric materials, This project will focus on lowering the power supply voltage of computing hardware as well as achieving non-volatile memory that can be directly integrated with the microprocessor.

Tsu-Jae K. Liu, Dean and Roy W. Carlson Professor of Engineering at the University of California, Berkeley and co-chair of the Northwest-AI-Hub, discussed the NW-AI-Hub's Workforce Development (WFD) efforts with testimony from postdocs and graduate students about their experiences.

Above image, from left to right: Tsu-Jae K. Liu, Maxwell Pauly, Sophie Tacher, Elam Day-Friedland, Lucy Revina, Vikram Jain

Sophie Tacher, Undergraduate Research Assistant at the UW Washington Nanofabrication Facility (WNF), shared her short course and cleanroom training experience.

Maxwell Pauly, MS student at the University of Hawaii at Manoa, described his tapeout course and chip design experience.

From UC Berkeley, Vikram Jain, Postdoc & Lecturer; Lucy Revina, MS student; and Elam Day-Friedland, Undergraduate Researcher, recounted their experiences organizing student-run electrical engineering courses through their IEEE student branch, designing chips in tapeout classes, and testing them in bring-up classes.

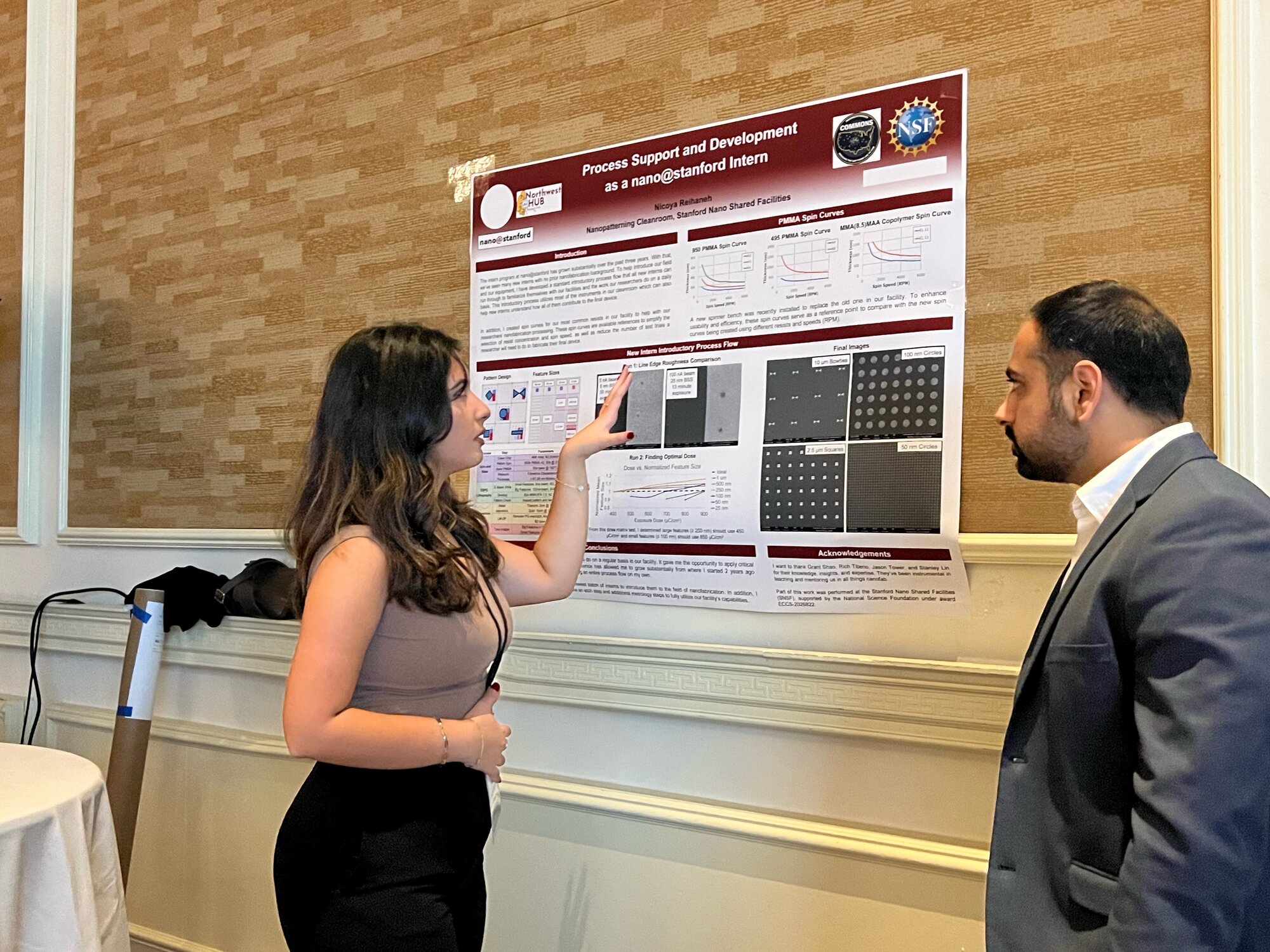

During the Poster session on October 29, Nicoya Reihaneh, an Undergraduate at San Jose State University and senior intern at the Stanford Nano Shared Facilities (SNSF), presented her poster on "Process Support and Development as a nano@stanford Intern" (pictured above).

Throughout the meeting, the Central Hub Office (Dr. Chorng-Ping Chang, Executive Director; Dr. Lequn Geng, Associate Director; Anna Lue, Program Manager) and Dr. Mary Tang, Managing Director of the Stanford Nanofabrication Lab (SNF) met and networked with many booth visitors. According to organizers, the event had almost 1000 registrants with additional live stream viewers.

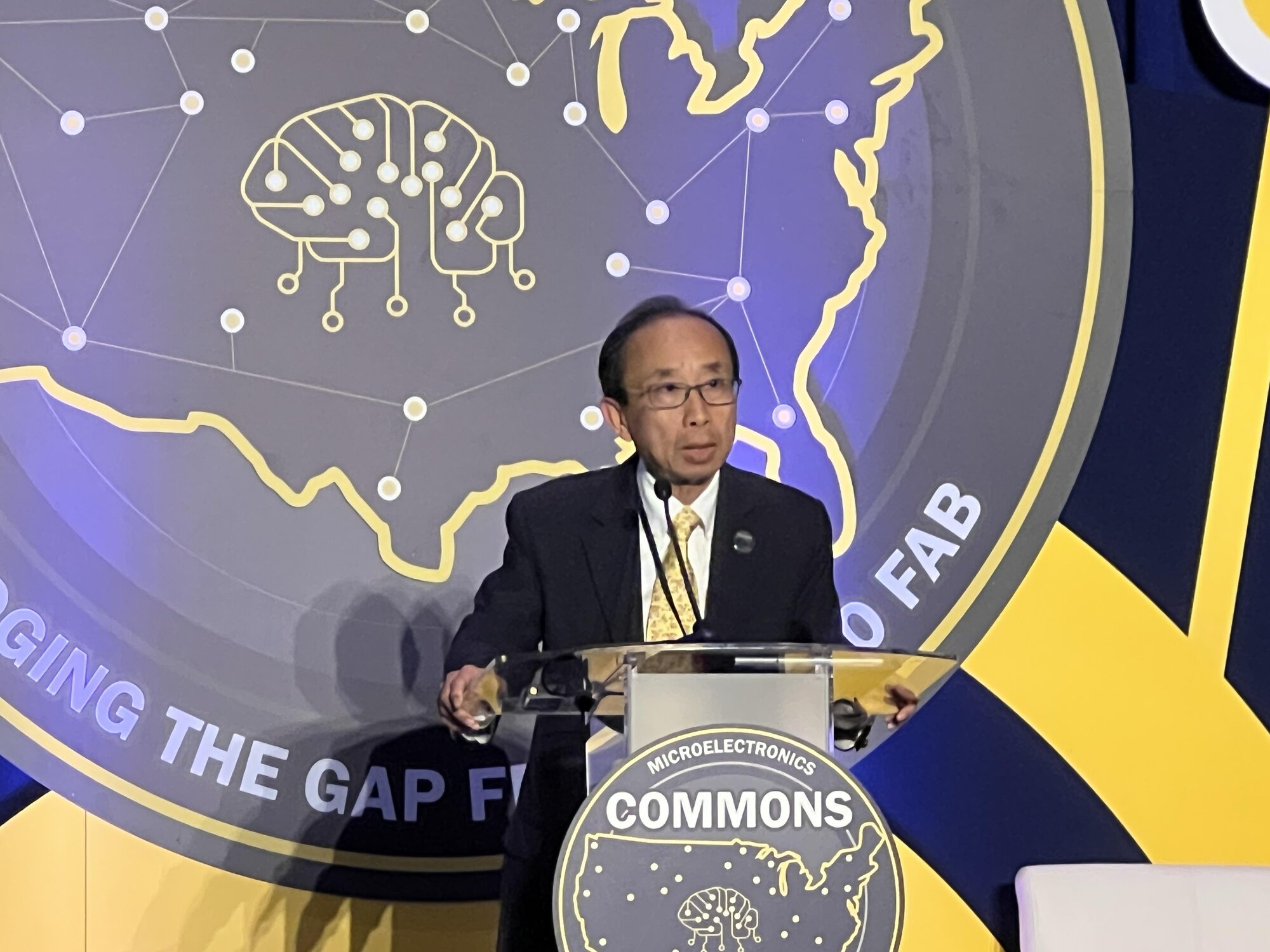

On the last day, H.-S. Philip Wong, Willard R. and Inez Kerr Bell Professor in the School of Engineering and chair of the Northwest-AI-Hub gave an overview on the Northwest-AI-Hub’s current status and future plans.

It was a delight meeting so many friends, new and old, and the Northwest-AI-Hub looks forward to seeing everyone next year!